# A 10/100 BASE-TX/ 100 BASE-FX Converter

(Port Mirror/Recovery, OAM Monitor/Controll, OAM PHY & RS232 Exentender)

# Features

Built in 3 MACs

- One external MII I/F port (P03)

- One external SMII/MII/RS232 I/F or internal MII I/F port (P02)

- One external SMII/MII/RS232 I/F or internal MII I/F port (P01)

Built in a 10/100BASE-TX/100BASE-FX

Transceiver

Built in a PHY for 100BASE-FX

- Built in a 3-port switch

- Non-blocking architecture

- 288Kb packet buffer

- 1K MAC address (or pass without address look up)

- Pass all packets with/without CRC check (optional)

- Pass PAUSE frame (optional)

- Support modified cut through frame forwarding for low latency

- Converter mode with auto-change mode function

- Support flow control for full duplex (symmetric/asymmetric) and half duplex (collision/carrier base) operation

- Bandwidth control (32K or 512Kbps x N)

- Forward 2046 bytes (max.) packets in switch mode

- 16 802.1Q tag VLANs (port base TAG insertion/ removal)

- OoS priority support (port or tag base)

- Port mirroring

- Link aggregation (support recovery)

- Offload setting for CPU port

Support Pass Through mode for extreme low latency data forwarding

- Pass all frames including OAM/ fragment

- Support 9K jumbo packets

Support RS232-like interface to TP/Fiber extension mode

- 2 independent pairs support

- Six MODEM control pins (RTS, CTS, DTR,

DSR, DC and SI)

Auto Baud rate detection (max. baud rate up to 500K bps)

Support special tag

Support TS-1000

- TS-1000 std. version 2

- IP113A/M/C/F maintenance frame compatible

- Variable and flexible auto loop back test

- OAM frame TX. /Rx. controllable

- OAM frame receiving notification

Support two wires serial CPU interface for management

- Configure local and remote IP113S through local SMI

- Monitor local and remote IP113S through local SMI

- PHY MII registers accessible

- Support loop back test (In-band or out-band)

- The OAM frame is compatible to TS-1000 standard (the Telecommunication Technology Committee, TTC)

Support RMON MIB Counters

- Ethernet statistics, Ethernet History, Alarm, Even groups

- Overflow interrupt supported

Support auto MDI-MDIX function (optional)

Support link fault pass through function between P01 and P02

Support far end fault function (FEF pattern or OAM)

Built in power abnormal detection

- LED display

- 4 modes selectable

- 4 blinking speed selectable

- Loop back test result display

Support EEPROM Configuration 0.25u technology, 2.5/3.3V power

Support Lead Free package (Please refer to the

Order Information)

# **General Description**

IP113S built in a 3-port switch controller, an OAM engine, a fast Ethernet transceiver, a PHY for 100BASE-FX and three MII I/F. Two of these MII can be configured as SMII or RS232 I/F. The powerful switch engine supports flow contol, VLAN, QoS, port mirroring, and trunking, etc. The transceivers in IP113S are designed in DSP approach with advance 0.25um technology; this results in high noise immunity and robust performance.

IP113S can be a 10/100BASE-TX to 100BASE-FX converter with an MII to connect to an external PHY for back up fiber application or an external MAC for web management application. IP113S forwards packets with length up to 2046 bytes in store and forward mode and modified cut through mode and it can support jumbo frame (up to 9K bytes) in pure converter mode and pass through mode to meet requirement of extra long packets.

IP113S supports remote access function and loop back test function defined in TS-1000 standard version 2 (\*). Local IP113S can access the registers of remote IP113S by programming local IP113S's registers via SMI connection. IP113S implements the management function using the maintenance frame defined in TS-1000 spec.

IP113S supports SMII to connect to a switch controller to build up a multiple-port fiber switch, which supports TS-1000. IP113S is a two-port 100BASE-FX PHY with TS-1000 function in this application.

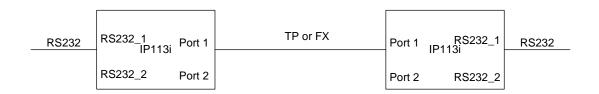

IP113S can be used as a six-pin RS232 extender, RTS, CTS, DTR, DSR, DC and SI, when it works as a RS232 to Ethernet converter. The limitation in distance of RS232 is extended to the distance of Ethenet 100BASE-TX or 100BASE-FX.

\* The Telecommunication Technology Committee owns the copyright of TS-1000.

# **Table of Contents**

| Features                                                                                               |   |

|--------------------------------------------------------------------------------------------------------|---|

| General Description                                                                                    |   |

| Table of Contents                                                                                      | 3 |

| Revision History                                                                                       |   |

| 1 Applications & Block diagram                                                                         |   |

| 1.1 Managed TX/FX converter, FX/FX repeater                                                            |   |

| 1.1.1 Store and forward / modified cut-through mode with internal PHY                                  |   |

| 1.1.2 Converter mode with internal PHY                                                                 |   |

| 1.1.3 Store and forward / modified cut-through mode with external PHY                                  |   |

| 1.1.4 Pass through mode (pure conerter without TS1000 function)                                        |   |

| 1.2 Dual Ethernet to RS232 converter                                                                   |   |

| 1.3 Dual PHY with OAM functions and MII or SMII I/F                                                    |   |

| 2 Pin Diagram                                                                                          |   |

| 3 Pin description                                                                                      |   |

| 4 Functional Description                                                                               |   |

| 4.1 Data forwarding                                                                                    |   |

| 4.2 Store & forward mode                                                                               |   |

| 4.3 Modified cut-through mode                                                                          |   |

| 4.4 Converter mode                                                                                     |   |

| 4.5 Pass through mode                                                                                  |   |

| 4.6 Operation mode summary                                                                             |   |

| <ul> <li>4.7 Switch engine and queue management</li> <li>4.7.1 Address learning and hashing</li> </ul> |   |

|                                                                                                        |   |

| 4.7.2     Aging       4.7.3     Special packet handling                                                |   |

| 4.7.3 Special packet handling                                                                          |   |

| 4.7.5 Packet buffer re-allocation                                                                      |   |

| 4.7.5 Flow Control                                                                                     |   |

| 4.7.7 Broadcast Storm Control.                                                                         |   |

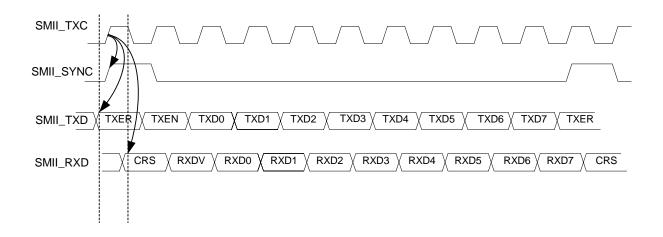

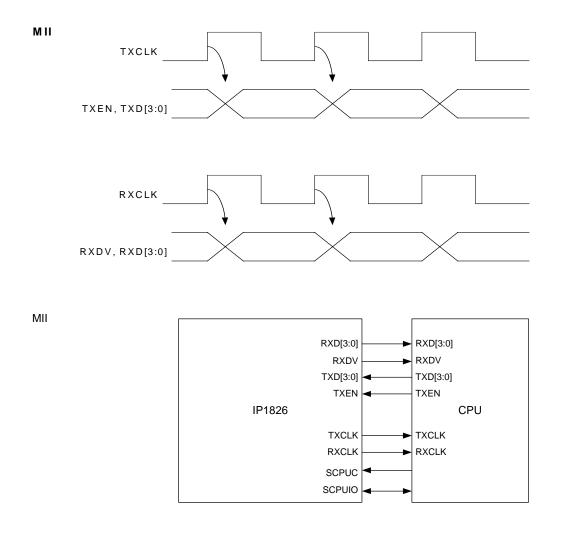

| 4.7.8 SMII, MI                                                                                         |   |

| 4.7.9 CPU interface                                                                                    |   |

| 4.7.10 Configure / access the port properties                                                          |   |

| 4.7.11 Force link                                                                                      |   |

| 4.7.12 Read / write MAC address table (LUT)                                                            |   |

| 4.7.13 Read / write PHY registers                                                                      |   |

| 4.7.14 EEPROM interface                                                                                |   |

| 4.7.15 MIBs counters                                                                                   |   |

| 4.7.16 Interrupt                                                                                       | 3 |

| 4.7.17 Reset                                                                                           |   |

| 4.7.18 LED                                                                                             | 3 |

| 4.8 Bandwidth Control                                                                                  | 3 |

| 4.9 VLAN                                                                                               |   |

| 4.9.1 Port_based VLAN                                                                                  |   |

| 4.9.2 Tag_based VLAN                                                                                   |   |

| 4.9.3 Add/ Remove/ Modify VLAN tag                                                                     |   |

| 4.9.4 Packet across a VLAN                                                                             |   |

| 4.10 Class of Service                                                                                  |   |

| 4.10.1 Port based CoS                                                                                  |   |

| 4.10.2 802.1Q priority tag based CoS                                                                   |   |

| 4.11 MAC address based Security                                                                        |   |

| 4.12 Port Mirroring (sniffer)                                                                          |   |

| 4.13 Trunk Channel                                                                                     | 3 |

| 4.13 | .1 Trunk channel behavior                                          | 3 |

|------|--------------------------------------------------------------------|---|

| 4.13 | .2 Load balance                                                    | 3 |

| 4.13 | .3 Use trunk channel function to implement redundant fiber channel | 3 |

| 4.14 | Special tag                                                        |   |

| 4.15 | Remote management                                                  | 3 |

| 4.15 | .1 OAM frame                                                       | 3 |

| 4.15 | .2 Remote monitor                                                  | 3 |

| 4.15 | .3 Remote control read/write                                       | 3 |

| 4.15 | .4 Auto sends (Status change notice)                               | 3 |

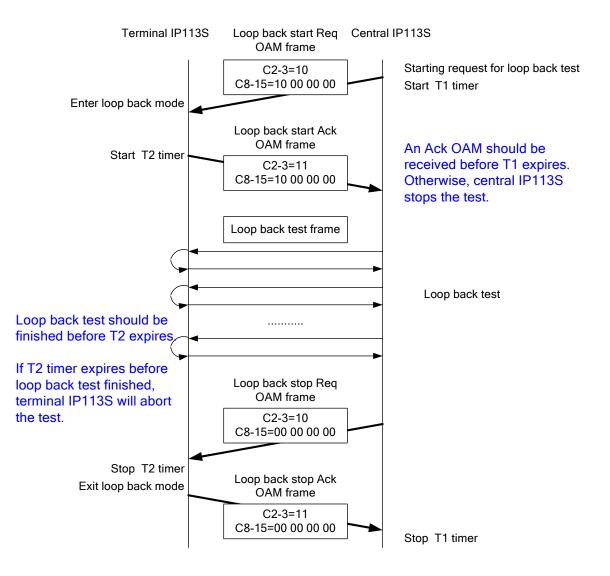

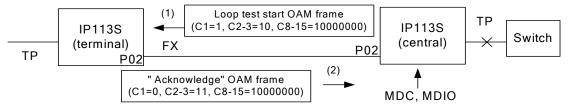

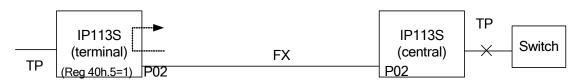

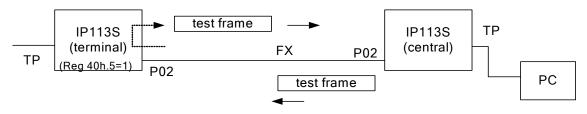

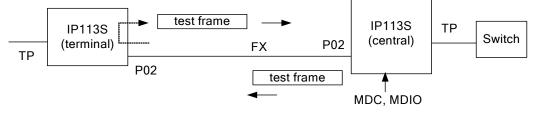

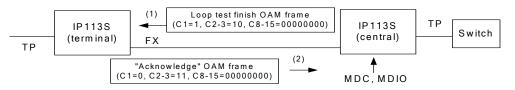

| 4.15 | .5 Loop back test                                                  | 3 |

| 4.16 | Link fault pass through                                            | 3 |

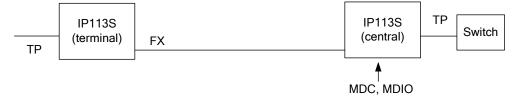

| 4.16 | .1 Normal case                                                     | 3 |

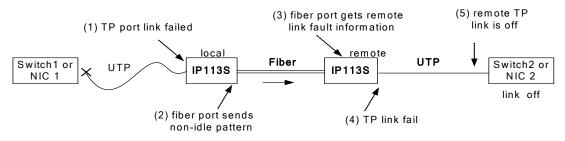

| 4.16 | .2 Remote TP port disconnected                                     | 3 |

| 4.16 | .3 FX port disconnected                                            | 3 |

| 4.16 |                                                                    | 3 |

| 4.16 | 5.5 Link fault pass through in FX to FX application                | 3 |

| 4.17 | RS232 extension                                                    |   |

| 5    | Register Map                                                       | 3 |

| 5.1  | MAC Control Register                                               | 3 |

| 5.2  | DMA Control register                                               | 3 |

| 5.3  | ARL Control Register                                               | 3 |

| 5.4  | SMI Control Register                                               |   |

| 5.5  | OAM Control Register                                               | 3 |

| 5.6  | Miscellaneous Control Register                                     |   |

| 5.7  | MIB Control Register                                               | 3 |

| 5.8  | PHY Register                                                       |   |

| 6    | Electrical Characteristics                                         |   |

| 6.1  | Absolute Maximum Rating                                            |   |

| 6.2  | AC Characteristics                                                 |   |

| 6.3  | DC Characteristics                                                 | 3 |

| 7    | Order Information                                                  | 3 |

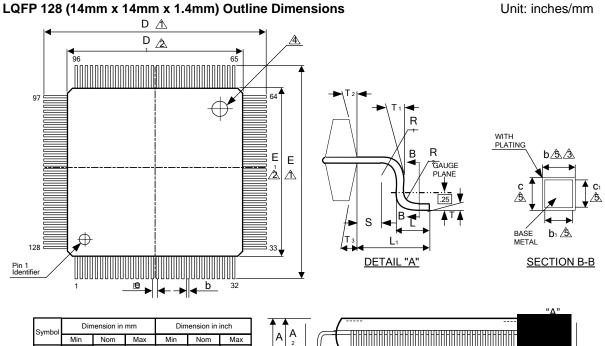

| 8    | Package Detail                                                     | 3 |

# **Revision History**

| Revision #    | -                | Change Description |

|---------------|------------------|--------------------|

| IP113S-DS-R01 | Initial release. |                    |

# 1 Applications & Block diagram

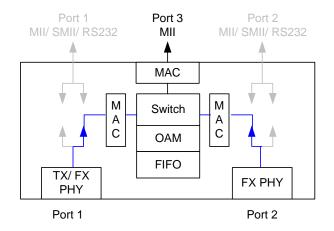

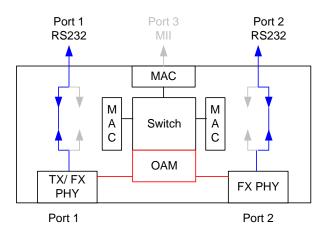

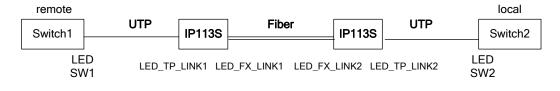

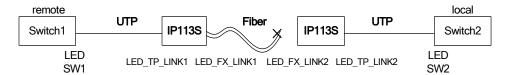

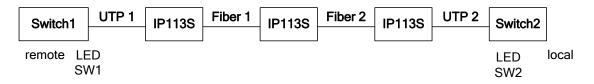

### 1.1 Managed TX/FX converter, FX/FX repeater

### 1.1.1 Store and forward / modified cut-through mode with internal PHY

| Function      | Setting                            | Pin setting                                                | Register value    |

|---------------|------------------------------------|------------------------------------------------------------|-------------------|

| OP Mode       | Switch / Modified cut-through mode | PassDis =1                                                 | 0B[2] = 0         |

|               |                                    | CFG_CutThrDis =don't care<br>CFG_CnvDis =1                 | 0B[1:0] = 00 / 10 |

| Dual PHY mode | Disabled                           | DulPHYDis = 1                                              | 0A[8] = 0         |

| Ext. MAC I/F  | Disabled                           | ExtIFDis1 = 1<br>ExtIFDis2 = 1                             | 0A[5:4] = 00      |

|               |                                    | Port1IFMd[1:0] = don't care<br>Port2IFMd[1:0] = don't care | 0A[3:0] = xxxx    |

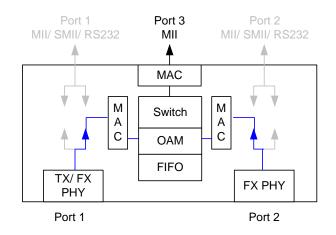

# 1.1.2 Converter mode with internal PHY

| Function      | Setting        | Pin setting                                                | Register value    |

|---------------|----------------|------------------------------------------------------------|-------------------|

| OP Mode       | Converter mode | PassDis = 1                                                | 0B[2] = 0         |

|               |                | CFG_CutThrDis = don't care<br>CFG_CnvDis = 0               | 0B[1:0] = 01 / 11 |

| Dual PHY mode | Disabled       | DulPHYDis = 1                                              | 0A[8] = 0         |

| Ext. MAC I/F  | Disabled       | ExtIFDis1 = 1<br>ExtIFDis2 = 1                             | 0A[5:4] = 00      |

|               |                | Port1IFMd[1:0] = don't care<br>Port2IFMd[1:0] = don't care | 0A[3:0] = xxxx    |

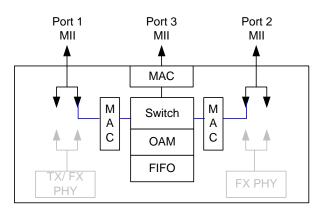

# 1.1.3 Store and forward / modified cut-through mode with external PHY

| Function      | Setting                            | Pin setting                                  | Register value     |

|---------------|------------------------------------|----------------------------------------------|--------------------|

| OP Mode       | Switch / Modified cut-through mode | PassDis = 1                                  | 0Bh[2] = 0         |

|               |                                    | CFG_CutThrDis = don't care<br>CFG_CnvDis = 1 | 0Bh[1:0] = 00 / 10 |

| Dual PHY mode | Disabled                           | DulPHYDis = 1                                | 0Ah[8] = 0         |

| Ext. MAC I/F  | МІІ                                | ExtIFDis1 = 0<br>ExtIFDis2 = 0               | 0Ah[5:4] = 11      |

|               |                                    | Port1IFMd[1:0] = 11<br>Port2IFMd[1:0] = 11   | 0Ah[3:0]=1111      |

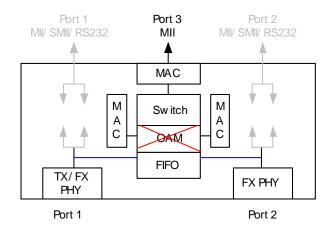

# 1.1.4 Pass through mode (pure conerter without TS1000 function)

| Function                                           | Setting  | Pin setting                                              | Register value |

|----------------------------------------------------|----------|----------------------------------------------------------|----------------|

| OP Mode Pass through mode (pure converter, no OAM) |          | PassDis = 0                                              | 0B[2] = 1      |

|                                                    |          | CFG_CutThrDis = don't care<br>CFG_CnvDis = don't care    | 0B[1:0] = xx   |

| Dual PHY mode                                      | Disabled | DulPHYDis = 1                                            | 0A[8] = 0      |

| Ext. MAC I/F                                       | Disabled | ExtIFDis1=1<br>ExtIFDis2=1                               | 0A[5:4]=00     |

|                                                    |          | Port1IFMd[1:0]= don't care<br>Port2IFMd[1:0]= don't care | 0A[3:0]=xxxx   |

# 1.2 Dual Ethernet to RS232 converter

| Function      | Setting        | Pin setting Register value                   |                    |

|---------------|----------------|----------------------------------------------|--------------------|

| OP Mode       | Converter mode | PassDis = 1                                  | 0Bh[2] = 0         |

|               |                | CFG_CutThrDis = don't care<br>CFG_CnvDis = 0 | 0Bh[1:0] = 00 / 10 |

| Dual PHY mode | Enabled        | DulPHYDis = 0                                | 0Ah[8] = 1         |

| Ext. MAC I/F  | RS232          | ExtIFDis1=0<br>ExtIFDis2=0                   | 0Ah[5:4]=11        |

|               |                | Port1IFMd[1:0]=00<br>Port2IFMd[1:0]=00       | 0Ah[3:0]=0000      |

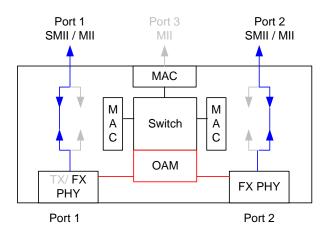

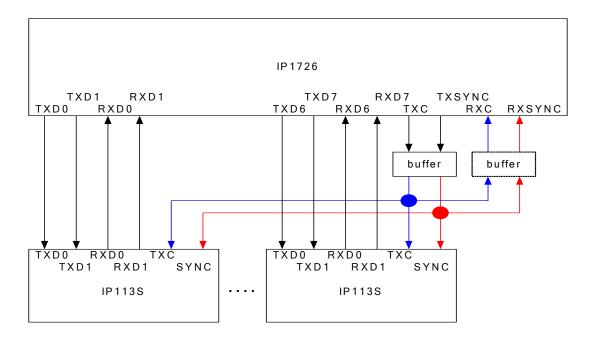

# 1.3 Dual PHY with OAM functions and MII or SMII I/F

| Function      | Setting            | Pin setting                                        | Register value                           |

|---------------|--------------------|----------------------------------------------------|------------------------------------------|

| OP Mode       | Converter mode     | PassDis = 1                                        | 0B[2] = 0                                |

|               |                    | CFG_CutThrDis = don't care<br>CFG_CnvDis = 0       | OB[1:0] = 00 / 10                        |

| Dual PHY mode | Enabled            | DulPHYDis = 0                                      | 0A[8] = 1                                |

| Ext. MAC I/F  | SMII/ Rev MII/ MII | ExtIFDis1=0<br>ExtIFDis2=0                         | 0A[5:4]=11                               |

|               |                    | Port1IFMd[1:0]=01,10,11<br>Port2IFMd[1:0]=01,10,11 | 0A[1:0]=01, 10, 11<br>0A[3:2]=01, 10, 11 |

IP113S Preliminary Data Sheet

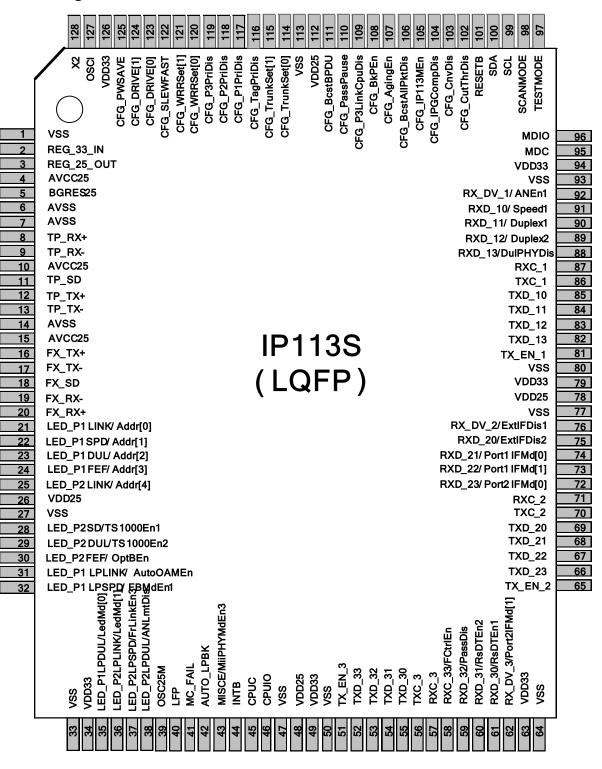

### 2 Pin Diagram

#### **Pin description**

| Туре | Description                |  |

|------|----------------------------|--|

| Р    | Power or ground            |  |

| I; O | I: Input pin; O:Output pin |  |

| IL   | Input latched upon reset   |  |

| Туре | Description                            |  |  |

|------|----------------------------------------|--|--|

| PD   | PD: Pulled down with internal resistor |  |  |

| PU   | PU: Pulled up with internal resistor   |  |  |

| I/O  | Bi-direction Input/Output              |  |  |

| Pin no.      | Label                                                                                   | Туре    | Description                                                                       |

|--------------|-----------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------|

| P1 MII/SMII/ | P1 MII/SMII/RS232 I/F (The following settings are latched at the end of power on Reset) |         |                                                                                   |

| 86           | TXC_1                                                                                   | I/O     | MII TXCLK / SMII TXC                                                              |

| 81           | TX_EN_1                                                                                 | I, PD   | MII TXEN / SMII SYNC / RS232 RD_1                                                 |

| 85           | TXD_10                                                                                  | I, PD   | MII TXD0 / SMII TXD1 / RS232 CTS_1                                                |

| 84           | TXD_11                                                                                  | I, PD   | MII TXD1/ RS232 DSR_1                                                             |

| 83           | TXD_12                                                                                  | I/O, PD | MII TXD2 / RS232 CD_1                                                             |

|              |                                                                                         |         | CD_1 is an output pin if RsDTEn1 is pulled low. Otherwise, it is an input pin.    |

| 82           | TXD_13                                                                                  | I/O, PD | MII TXD3 / RS232 RI_1                                                             |

|              |                                                                                         |         | RI_1 is an output pin if RsDTEn1 is pulled low.<br>Otherwise, it is an input pin. |

| 87           | RXC_1                                                                                   | I/O     | MII RXCLK / SMII RXC                                                              |

| Pin no.      | Label                                                                        | Туре    | Description                                                                                                                                                                                                                                                        |  |  |

|--------------|------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P1 MII/SMII/ | /RS232 I/F (The following settings are latched at the end of power on Reset) |         |                                                                                                                                                                                                                                                                    |  |  |

| 92           | RX_DV_1/ANEn1                                                                | I/O, PU | MII RXDV /SMII RXSYNC/ RS232 TD_1                                                                                                                                                                                                                                  |  |  |

|              |                                                                              |         | <b>P1 nway enable</b><br>0: nway disabled<br>1: nway enabled (default)<br>The setting can be updated by writing 4Eh[2].                                                                                                                                            |  |  |

| 91           | RXD_10/Speed1                                                                | I/O, PU | MII RXD0 / SMII RXD1 / RS232 RTS_1                                                                                                                                                                                                                                 |  |  |

|              |                                                                              |         | <b>P1 speed mode</b><br>0: 10Mb speed<br>1: 100Mb speed (default)<br>The setting can be updated by writing 4Eh[3].                                                                                                                                                 |  |  |

| 90           | RXD_11/Duplex1                                                               | I/O, PU | MII RXD1 / RS232 DTR_1                                                                                                                                                                                                                                             |  |  |

|              |                                                                              |         | <b>P1 duplex mode</b><br>0: half duplex<br>1: full duplex (default)<br>The setting can be updated by writing 4Eh[4].                                                                                                                                               |  |  |

| 89           | RXD_12/Duplex2                                                               | I/O, PU | MII RXD2                                                                                                                                                                                                                                                           |  |  |

|              |                                                                              |         | <b>P2 duplex mode</b><br>0: half duplex<br>1: full duplex (default)<br>The setting can be updated by writing 4Eh[8].                                                                                                                                               |  |  |

| 88           | RXD_13/DulPHYDis                                                             | I/O, PU | MII RXD3                                                                                                                                                                                                                                                           |  |  |

|              |                                                                              |         | <ul> <li>IP113S Dul PHY mode disable</li> <li>0: P1 and p2 work as two independent PHY with OAM function</li> <li>1: P1and p2 are interconnected through internal switch engine or FIFO (default)</li> <li>The setting can be updated by writing 0Ah[8]</li> </ul> |  |  |

| Pin no.                                                                               | Label   | Туре    | Description                                                                       |  |

|---------------------------------------------------------------------------------------|---------|---------|-----------------------------------------------------------------------------------|--|

| P2 MII/SMII/RS232 I/F (The following settings are latched at the end of power on Rese |         |         |                                                                                   |  |

| 70                                                                                    | TXC_2   | I/O     | MII TXCLK                                                                         |  |

| 65                                                                                    | TX_EN_2 | I, PD   | MII TXEN / RS232 RD_2                                                             |  |

| 69                                                                                    | TXD_20  | I, PD   | MII TXD0 / SMII TXD2/ RS232 CTS_2                                                 |  |

| 68                                                                                    | TXD_21  | I, PD   | MII TXD1 / RS232 DSR_2                                                            |  |

| 67                                                                                    | TXD_22  | I/O, PD | MII TXD2 / RS232 CD_2                                                             |  |

|                                                                                       |         |         | CD_2 is an output pin if RsDTEn2 is pulled low. Otherwise, it is an input pin.    |  |

| 66                                                                                    | TXD_23  | I/O, PD | MII TXD3 / RS232 RI_2                                                             |  |

|                                                                                       |         |         | RI_2 is an output pin if RsDTEn2 is pulled low.<br>Otherwise, it is an input pin. |  |

| 71                                                                                    | RXC_2   | I/O     | SMII RXC                                                                          |  |

| Pin no.      | Label                         | Туре        | Description                                                                                                                                                                                                                                                            |

|--------------|-------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2 MII/SMII/ | RS232 I/F (The following sett | ings are la | atched at the end of power on Reset)                                                                                                                                                                                                                                   |

| 76           | RX_DV_2/ExtIFDis1             | I/O, PU     | MII RXDV / RS232 TD_2                                                                                                                                                                                                                                                  |

|              |                               |             | P1 external I/F disable<br>0: external MAC interface enable. Using<br>external MII or SMII or RS232 interface<br>defined in bit[3:0].<br>1: using internal MII interface connected to<br>internal PHY (default)<br>The setting can be updated by writing 0Ah[4]        |

| 75           | RXD_20/ExtIFDis2              | I/O, PU     | MII RXD0 / SMII RXD2/ RS232 RTS_2                                                                                                                                                                                                                                      |

|              |                               |             | <b>P2 external I/F disable</b><br>0: external MAC interface enable. Using<br>external MII or SMII or RS232 interface<br>1: using internal MII interface connected to<br>internal PHY (default)<br>The setting can be updated by writing 0Ah[3]                         |

| 74           | RXD_21/Port1IFMd[0]           | I/O, PU     | MII RXD1/ RS232 DTR_2                                                                                                                                                                                                                                                  |

| 73           | RXD_22/Port1IFMd[1]           | I/O, PU     | P1 external I/F mode[0]                                                                                                                                                                                                                                                |

|              |                               |             | MII RXD2<br>P1 external I/F mode[1]                                                                                                                                                                                                                                    |

|              |                               |             | Port1IFMd[1:0]<br>00: RS232<br>01: SMII<br>10: reversed MII<br>11: MII (default)<br>Note: Only MII/reversed-MII interface can<br>connected to internal PHY or MAC, others to<br>PHY only.<br>The setting can be updated by writing 0Ah[1:0]                            |

| 72           | RXD_23/Port2IFMd[0]           | I/O, PU     | MII RXD3                                                                                                                                                                                                                                                               |

|              |                               |             | P2 external I/F mode[0]<br>Port2IFMd[1:0]<br>00: RS232<br>01: SMII<br>10: reversed MII<br>11: MII (default)<br>Note: Only MII/reversed-MII interface can<br>connected to internal PHY or MAC, others to<br>PHY only.<br>The setting can be updated by writing 0Ah[3:2] |

| Pin no.       | Label                          | Туре    | Description                                                                                                                                             |

|---------------|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3 MII I/F (T | he following settings are late |         |                                                                                                                                                         |

| 56            | TXC_3                          | I/O     | MII TXCLK                                                                                                                                               |

| 51            | TX_EN_3                        | I, PD   | MII TXEN                                                                                                                                                |

| 55            | TXD_30                         | I, PD   | MII TXD0                                                                                                                                                |

| 54            | TXD_31                         | I, PD   | MII TXD1                                                                                                                                                |

| 53            | TXD_32                         | I, PD   | MII TXD2                                                                                                                                                |

| 52            | TXD_33                         | I, PD   | MII TXD3                                                                                                                                                |

| 57            | RXC_3                          | I/O     | MII RXC                                                                                                                                                 |

| 62            | RX_DV_3/Port2IFMd[1]           | I/O, PU | MII RXDV<br>P2 external I/F mode[1]<br>Please refer to RXD_23/Port2IFMd[0].                                                                             |

| 61            | RXD_30/RsDTEn1                 | I/O, PU | MII RXD0<br>P1 RS232 DTE mode enable<br>0: RS232 is in DCE mode. CD_1 and RI_1 are<br>outputs.<br>1: RS232 is in DTE mode. CD_1 and RI_1 are<br>inputs. |

|               |                                |         | <b>P1 SMII RXD delay</b><br>1: SMII RXD delay 4ns (default)<br>0: no delay<br>The setting can be updated by writing 0Ah[6]                              |

| 60            | RXD_31/RsDTEn2                 | I/O, PU | MII RXD1<br>P2 RS232 DTE mode enable<br>0: RS232 is in DCE mode. CD_2 and RI_2 are<br>outputs.<br>1: RS232 is in DTE mode. CD_2 and RI_2 are<br>inputs. |

|               |                                |         | <b>P2 SMII RXD delay</b><br>1: SMII RXD delay 4ns (default)<br>0: no delay<br>The setting can be updated by writing 0Ah[7]                              |

| 59            | RXD_32/PassDis                 | I/O, PU | MII RXD2                                                                                                                                                |

|               |                                |         | Pass through mode diable<br>0: Pass through mode enable<br>1: Pass through mode disable (default)<br>The setting can be updated by writing 0BH[2]       |

| 58            | RXD_33/FCtrlEn                 | I/O, PU | MII RXD3<br>IP113S flow control enable<br>0: disable<br>1: enable (default)<br>The setting can be updated by writing 33H[5:0]                           |

| Pin no.     | Label                                                  | Туре      | Description                                                                                                         |

|-------------|--------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------|

| LED display | (The following settings are I                          | atched at | the end of power on Reset)                                                                                          |

| 21          | LED_P1LINK/Addr[0]                                     | I/O, PD   | P1 LINK/ACT LED                                                                                                     |

|             |                                                        |           | P1 PHY_addr[0]<br>(default = 0)                                                                                     |

| 22          | LED_P1SPD/Addr[1]                                      | I/O, PD   | P1 Speed/SD LED                                                                                                     |

|             |                                                        |           | P1 PHY_addr[1]<br>(default = 0)                                                                                     |

| 23          | LED_P1DUL/Addr[2]                                      | I/O, PD   | P1 Duplex/Col LED                                                                                                   |

|             |                                                        |           | P1 PHY_addr[2]<br>(default = 0)                                                                                     |

| 24          | LED_P1FEF/Addr[3]                                      | I/O, PD   | P1 FEF/Loop Back LED                                                                                                |

|             |                                                        |           | P1 PHY_addr[3]<br>(default = 0)                                                                                     |

| 25          | LED_P2LINK/Addr[4]                                     | I/O, PD   | P2 LINK/ACT LED                                                                                                     |

|             |                                                        |           | P1 PHY_addr[4]<br>(default = 0)                                                                                     |

|             | P2 PHY_addr[4:0] = P1 PHY<br>P3 PHY_addr[4:0] = P1 PHY |           |                                                                                                                     |

| 28          | LED_P2SD/TS1000En1                                     | I/O, PU   | P2 fiber Signal Detect LED                                                                                          |

|             |                                                        |           | <b>P1 TS1000 enable</b><br>0: disable<br>1: enable (default)<br>The setting can be updated by writing 39h[0]        |

| 29          | LED_P2DUL/TS1000En2                                    | I/O, PU   | P2 Duplex/Col LED                                                                                                   |

|             |                                                        |           | <b>P2 TS1000 enable</b><br>0: disable<br>1: enable (default)<br>The setting can be updated by writing 39h[1]        |

| 30          | LED_P2FEF/OptBEn                                       | I/O, PU   | P2 FEF/ Loop back LED                                                                                               |

|             |                                                        |           | <b>Option B enable</b><br>0: disable<br>1: enable <b>(</b> default)<br>The setting can be updated by writing 39h[2] |

| 31          | LED_P1LPLINK/AutoOAM<br>En                             | I/O, PU   | P1 Link Partner's Link/Test                                                                                         |

|             |                                                        |           | Auto send enable<br>0: enable<br>1: disable (default).<br>The setting can be updated by writing 39h[3]              |

IP113S Preliminary Data Sheet

| Pin no.     | Label                         | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED display | (The following settings are I | atched at | the end of power on Reset)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32          | LED_P1LPSPD/FBMdEn1           | I/O, PU   | P1 Link Partner's Speed/Test Done<br>TP port fiber mode eable<br>0: enable<br>1: disable (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 35          | LED_P1LPDUL/LedMd[0]          | I/O, PU   | P1 Link Partner's Duplex LED/Test OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 36          | LED_P2LPLINK/LedMd[1]         | I/O, PU   | LED mode[0]<br>P2 Link Partner's Link LED /Test<br>LED mode[1]<br>LED mode[1:0]<br>00 Bi-colors speed mode* / duplex(col) /<br>FEF(loop)<br>01 Link100(act)/ link10(act)/ duplex/ FEF<br>10 Link100(act)/ link10(act)/ duplex(col)/<br>FEF(loop)<br>11 Link(act)/ speed/ duplex(col)/<br>FEF(loop) (default)<br>The setting can be updated by writing<br>01h[12:11]<br>* : when bi-color mode enabled, first two LED<br>signals are combined to drive the bi-color<br>LEDs. Link100(act)-> color one, Link10(act) or<br>FEF (in fiber)-> color two. |

|             |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 37          | LED_P2LPSPD/FrLinkEn3         | I/O, PU   | P2 Link Partner's Speed /Test Done<br>P3 force link enable<br>0: enable<br>1: disable (default)<br>The setting can be updated by writing 35h[7]                                                                                                                                                                                                                                                                                                                                                                                                     |

| 38          | LED_P2LPDUL/ANLmtDis          | I/O, PU   | P2 Link Partner's Duplex /Test OK<br>Nway capability limited disable<br>0: limited<br>1: not limited (default)<br>The setting can be updated by writing 30h[3]                                                                                                                                                                                                                                                                                                                                                                                      |

### LED functions

|              | LED Mode                                                          |                                                                 |                                                                                 |                                                                   |

|--------------|-------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------|

| LED pin      | 00                                                                | 01                                                              | 10                                                                              | 11 (default)                                                      |

| LED_P1LINK   | -Dual color mode                                                  | On: Link 100M<br>Off: Unlink<br>Flash: 100M Act<br>On: Link 10M | On: Link 100M<br>Off: Unlink<br>Flash: 100MAct                                  | On: Link<br>Off: Unlink<br>Flash: Act<br>On: 100M                 |

| LED_P1SPD    |                                                                   | Off: Unlink<br>Flash: 10MAct                                    | On: Link 10M<br>Off: Unlink<br>Flash: 10M Act                                   | Off: 10M                                                          |

| LED_P1DUL    | On: Full<br>Off: Half<br>Flash: Collision                         | On: Full<br>Off: Half                                           | On: Full<br>Off: Half<br>Flash: Collision                                       | On: Full<br>Off: Half<br>Flash: Collision                         |

| LED_P1FEF    | On: FEF detected<br>Off: No FEF<br>Flash: Enter loop<br>back mode | On: FEF detected<br>Off: No FEF                                 | On: FEF detected<br>Off: No FEF<br>Flash: Enter loop<br>back mode               | On: FEF detected<br>Off: No FEF<br>Flash: Enter loop<br>back mode |

| LED_P2LINK   | -Dual color mode                                                  | On: Link 100M<br>Off: Unlink<br>Flash: 100M Act                 | On: Link 100M<br>Off: Unlink<br>Flash: 100MAct                                  | On: Link<br>Off: Unlink<br>Flash: Act                             |

| LED_P2SD     |                                                                   | On: Link 10M<br>Off: Unlink<br>Flash: 10MAct                    | On: Link 10M<br>Off: Unlink<br>Flash: 10M Act                                   | On: 100M<br>Off: 10M                                              |

| LED_P2DUL    | On: Full<br>Off: Half<br>Flash: Collision                         | On: Full<br>Off: Half                                           | On: Full<br>Off: Half<br>Flash: Collision                                       | On: Full<br>Off: Half<br>Flash: Collision                         |

| LED_P2FEF    | On: FEF detected<br>Off: No FEF<br>Flash: Enter loop<br>back mode | On: FEF detected<br>Off: No FEF                                 | On: FEF detected<br>Off: No FEF<br>Flash: Enter loop<br>back mode               | On: FEF detected<br>Off: No FEF<br>Flash: Enter loop<br>back mode |

|              | Normal operation                                                  |                                                                 | When performing A                                                               | uto Loop Back test                                                |

| LED_P1LPLINK | On: Link partner Link<br>Off: Link partner Unli                   |                                                                 |                                                                                 | enable. IP113S asks                                               |

| LED_P1LPSPD  | On: Link partner is 100M<br>Off: Link partner is 10M              |                                                                 | On: Loop back test complete<br>Off: Under loop back test                        |                                                                   |

| LED_P1LPDUL  | On: Link partner is Full<br>Off: Link partner is Half             |                                                                 | On: Pass Loop back test<br>Off: Fail Loop back test                             |                                                                   |

| LED_P2LPLINK | On: Link partner Link ok<br>Off: Link partner Unlink              |                                                                 | Flash: Auto loop test enable. IP113S asks link partner to enter loop back mode. |                                                                   |

| LED_P2LPSPD  | On: Link partner is 100M<br>Off: Link partner is 10M              |                                                                 | On: Loop back test complete<br>Off: Under loop back test                        |                                                                   |

| LED_P2LPDUL  | On: Link partner is Fu<br>Off: Link partner is Ha                 |                                                                 | On: Pass Loop back<br>Off: Fail Loop back te                                    |                                                                   |

#### Dual color mode LED

|                  | LED_P1LINK (LED_P2LINK) | LED_P1SPEED (LED_P2SPD) |

|------------------|-------------------------|-------------------------|

| Link off         | 1                       | 1                       |

| 100M link        | 1                       | 0                       |

| 100M link/Active | Flash                   | 0                       |

| 10M link         | 0                       | 1                       |

| 10M link/Active  | 0                       | Flash                   |

| Pin no.       | Label                       | Туре      |                                                                    | Descr              | ription                                                                                              |

|---------------|-----------------------------|-----------|--------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------|

| Configuration | (The following settings are | e latched | at the end of                                                      | power on           | Reset)                                                                                               |

| 102           | CFG_CutThrDis               | I, PU     |                                                                    |                    | mode disable                                                                                         |

| 103           | CFG_CnvDis                  | I, PU     | Converter n                                                        | node disal         | ble                                                                                                  |

|               |                             |           | CFG_Cut<br>ThrDis                                                  | CFG_C<br>nvDis     | Function                                                                                             |

|               |                             |           | 1                                                                  | 1                  | Store and forward mode (default)                                                                     |

|               |                             |           | 0                                                                  | 1                  | Modified cut-through mode                                                                            |

|               |                             |           | 1                                                                  | 0                  | Converter mode                                                                                       |

|               |                             |           | 0                                                                  | 0                  | Converter mode if<br>duplex and speed of<br>P01 equal P02,<br>otherwise modified<br>cut-through mode |

|               |                             |           | The setting of                                                     | can be upd         | ated by writing 0Bh[1:0]                                                                             |

| 104           | CFG_IPGCompDis              | I, PU     | IPG comper<br>0: Tx.IPG+8<br>1: Tx.IPG+0<br>The setting of         | Oppm<br>ppm (defau |                                                                                                      |

| 105           | CFG_IP113MEn                | I, PU     | 0: disable<br>1: enable (de                                        | efault)            | e IP113A/M OAM<br>lated by writing 39h[4]                                                            |

| 106           | CFG_BcstAllPktDis           | I, PU     | Broadcast a<br>0: enable<br>1: disable (d                          |                    | d frame disable                                                                                      |

| 107           | CFG_AgingEn                 | I, PU     | MAC addres<br>0: disable<br>1: enable (de<br>The setting of        | efault)            | ging enable<br>lated by writing 12H[1]                                                               |

| 108           | CFG_BkPEn                   | I, PU     | 0: disable<br>1: enable (de                                        | -<br>efault)       | ssure enable<br>lated by writing 34h[2:0]                                                            |

| 109           | CFG_P3LinkCpuDis            | I, PU     | <b>P3 link to C</b><br>0: enable<br>1: disable (d<br>The setting o | efault)            | e<br>lated by writing 12h[3]                                                                         |

| 110           | CFG_PassPause               | I, PU     | Pass PAUS<br>0: enable<br>1: disable (d<br>The setting o           | efault)            | ated by writing 33h[5:0]                                                                             |

| Pin no.       | Label                       | Туре  | Description                                                                                                                                             |

|---------------|-----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration | (The following settings are |       | at the end of power on Reset)                                                                                                                           |

| 111           | CFG_BcstBPDU                | I, PU | Broadcast BPDU frames<br>0: discarded<br>1: broadcasting (default)<br>The setting can be updated by writing 01H[4]                                      |

| 114           | CFG_TrunkSet[0]             | I, PU | Trunk setting [1:0]                                                                                                                                     |

| 115           | CFG_TrunkSet[1]             | I, PU | CFG_TrunkSet[1:0]<br>00:Port2 and Port3 Trunk<br>01:Port1 and Port3 Trunk<br>10:Port1 and Port2 Trunk<br>11:No Trunk (default)                          |

| 116           | CFG_TagPriDis               | I, PU | <b>TAG priority disable</b><br>0: enable<br>1: disable (default)<br>The setting can be updated by writing 08H[4]                                        |

| 117           | CFG_P1PriDis                | I, PU | P1 port based priority disable<br>0:enable<br>1: disable (default)<br>The setting can be updated by writing 08H[0]                                      |

| 118           | CFG_P2PriDis                | I, PU | <b>P2 port based priority disable</b><br>0: enable<br>1: disable (default)<br>The setting can be updated by writing 08H[1]                              |

| 119           | CFG_P3PriDis                | I, PU | <b>P3 port based priority disable</b><br>0: enable<br>1: disable (default)<br>The setting can be updated by writing 08H[2]                              |

| 120           | CFG_WRRSet[0]               | I, PD | WRR Ratio[1:0]                                                                                                                                          |

| 121           | CFG_WRRSet[1]               | I, PD | 00:First in first out (default)<br>01:High priority: Low priority = 2:1<br>10:High priority: Low priority = 4:1<br>11:High priority: Low priority = 8:1 |

| 122           | CFG_SLEWFAST                | I, PD | PAD slew rate fast enable<br>0: enable (default)<br>1: disable                                                                                          |

| 123           | CFG_DRIVE[0]                | I, PD | PAD output driving current [1:0]                                                                                                                        |

| 124           | CFG_DRIVE[1]                | I, PD | CFG_DRIVE[1:0]<br>00: 2mA (default)<br>01: 4mA<br>10: 8mA<br>11: 12mA                                                                                   |

| 125           | CFG_PWSAVE                  | I, PD | <b>Power saving mode enable</b><br>0: enable (default)<br>1: disable                                                                                    |

Copyright © 2005, IC Plus Confidential.

| Pin no.       | Label                 | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|-----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration | n (Real time setting) |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 40            | LFP                   | I, PD      | Linlk fault pass through<br>0: disable (default)<br>1:enable<br>Link status of one port is forwarded to the<br>other port.<br>This pin is real time setting instead of the<br>latched value at the end of reset.<br>The setting can be updated by writing 39H[15]                                                                                                                                                                                                        |

| 41            | MC_FAIL               | I, PD      | <b>Media converter fails</b><br>0: normal (default)<br>1: fail<br>The setting can be updated by writing 39H[8]                                                                                                                                                                                                                                                                                                                                                           |

| 42            | AUTO_LPBK             | I, PD      | Auto loop back test<br>0: disable (default)<br>1:enable<br>A port will perform loop back test for once if its<br>corresponding TS1000En pin is pulled high<br>and there is a low-to-high transition on this pin.<br>The corresponding LED pin LED_PxLPLINK is<br>always flashing if this pin stays at high.<br>It provides an easy way to instruct IP113M<br>performing loop back test without<br>programming registers.<br>The setting can be updated by writing 40H[4] |

| 43            | MISCE/MiiPHYMdEn3     | I/O,<br>PU | <b>P3 MII I/F PHY mode_enable</b><br>0: MAC mode<br>1: PHY mode (default)                                                                                                                                                                                                                                                                                                                                                                                                |

| Pin no. | Label  | Туре | Description              |

|---------|--------|------|--------------------------|

| MDI     |        |      |                          |

| 8       | TP_RX+ | I    | TP receive pair          |

| 9       | TP_RX- | I    | TP receive pair          |

| 11      | TP_SD  | I    | 100Base-FX signal detect |

| 12      | TP_TX+ | 0    | TP transmit pair         |

| 13      | TP_TX- | 0    | TP transmit pair         |

| 16      | FX_TX+ | 0    | Fiber transmit pair      |

| 17      | FX_TX- | 0    | Fiber transmit pair      |

| 18      | FX_SD  | I    | 100Base-FX signal detect |

| 19      | FX_RX+ | I    | Fiber receive pair       |

| 20      | FX_RX- | I    | Fiber receive pair       |

| Pin no.    | Label    | Туре    | Description                                                                                                                                                    |

|------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI        | ·        |         |                                                                                                                                                                |

| 95         | MDC      | I/O     | <b>Clock for serial management bus.</b><br>It's recommended to add a 30pf capacitor to<br>ground for noise filetrring.                                         |

| 96         | MDIO     | I/O     | <b>I/O data for serial manment bus</b> .<br>It's recommended to add a 4.7K pull up<br>resistor connecting to VDD and a 30pf<br>capacitor connecting to ground. |

| EEPROM I   | nterface |         |                                                                                                                                                                |

| 99         | SCL      | I/O, PU | Serial EEPROM clock output                                                                                                                                     |

| 100        | SDA      | I/O, PU | Serial EEPROM data                                                                                                                                             |

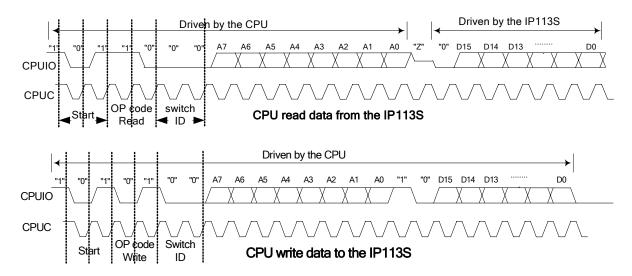

| CPU Interf | ace      |         |                                                                                                                                                                |

| 45         | CPUC     | I       | Serial CPU access clock input.<br>Please see the section of "Programming the<br>Internal Register" for the usage of SCPUC<br>and SCPUIO.                       |

| 46         | CPUIO    | I/O, PU | Serial CPU data                                                                                                                                                |

| 44         | INTB     | O, PU   | Interrupt<br>0: an interrupt happens.<br>1: no interrupt.                                                                                                      |

| Pin no.       | Label      | Туре  | Description                                                                                                                                  |

|---------------|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Miscellaneous |            |       |                                                                                                                                              |

| 101           | RESETB     | I     | System reset (low active).<br>It should be kept at "low" for at least 10<br>microseconds.                                                    |

| 127           | OSCI       | I     | Crystal/ Oscillator 25MHz input                                                                                                              |

| 128           | X2         | 0     | Crystal output                                                                                                                               |

| 39            | OSC25M     | 0     | A 25Mhz reference clock output for other devices                                                                                             |

| 5             | BGRES25    | I     | <b>Band gap resister</b><br>It is connected to GND throught a 6.19k(1%)<br>resistor in application citcuit                                   |

| 2             | REG_33_IN  | I     | 3.3V Power                                                                                                                                   |

| 3             | REG_25_OUT | 0     | <b>Regulat output</b><br>The interal linear regulator uses this pin to<br>control external transistor to generates a<br>voltages source 2.5V |

| Test mode     |            |       |                                                                                                                                              |

| 97            | TESTMODE   | I, PD | <b>TEST pin</b><br>This pin shold be left open or connected to<br>ground for normal operation                                                |

| 98            | SCANMODE   | I, PD | <b>Scan pin</b><br>This pin shold be left open or connected to<br>ground for normal operation                                                |

| Pin no.                                                  | Label  | Туре | Description   |

|----------------------------------------------------------|--------|------|---------------|

| Power                                                    |        |      |               |

| 4<br>10<br>15                                            | AVCC25 |      | Analog Power  |

| 26<br>48<br>78<br>112                                    | VDD25  |      | Digital Power |

| 34<br>49<br>63<br>94<br>79<br>126                        | VDD33  |      | Digital Power |

| 1<br>27<br>33<br>47<br>50<br>64<br>77<br>80<br>93<br>113 | VSS    |      |               |

| 6<br>7<br>14                                             | AVSS   |      |               |

# 3 Functional Description

#### 3.1 Data forwarding

Related registers 0Bh[1:0].

IP113S supports four types of data forwarding mode, store & forward mode, modified cut-through mode, converter mode and pure converter mode. User can select one of the modes by programming register 0Bh[1:0].

#### 3.2 Store & forward mode

| oiz otoro a rorman |        |  |

|--------------------|--------|--|

| Related registers  | 01h[5] |  |

When IP113S works in "store & forward" mode, it begins to forward a packet to a destination port after the entire packet is received. The latency depends on the packet length. The maximum packet length is up to 2046 bytes in this mode. Different from a normal switch chip, IP113S supports options to forward IEEE802.3x pause frame. These options are default off and can be turned on by programming register 01h[5].

#### 3.3 Modified cut-through mode

IP113S begins to forward the received data when it receives the first 64 bytes of the frame. The latency is about 512 bits time width. The maximum packet length is up to 2046 bytes in this mode. IP113S filters OAM frames in this mode. Please refer to pin description of pin 102 CFG\_CutThrDis and pin 103 CFG\_CnvDis or register 0Bh[1:0] for configuration information.

#### 3.4 Converter mode

IP113S operates with small latency in this mode. The transmission flow does not wait until entire frame is ready, but instead it forwards the received data immediately after the data being received. Both transceivers in IP113S are interconnected via OAM engine and the internal switch engine and data buffer are not used. IP113S filters OAM farms and supports 9KB jumbo packet in this mode. Please refer to pin description of 102 CFG\_CutThrDis and pin 103 CFG\_CnvDis or register 0Bh[1:0] for configuration information. The switch engine in IP113S is disabled in this mode.

#### 3.5 Pass through mode

IP113S operates with the minimum latency in this mode. Both transceivers in IP113S are interconnected via internal MIIs and the internal switch engine and data buffer are not used. IP113S pass all frames including OAM farms and supports 9KB jumbo packet in this mode. Please refer to pin description of PassDis or register 0Bh[2] for configuration information. The switch engine in IP113S is disabled in this mode. IP113S doesn't support TS1000 when working in this mode.

In converter mode or pass through mode, it is strongly recommended that both TP port and fiber port of IP113S should work at 100M full duplex.

# 3.6 Operation mode summary

|   | 0Bh<br>[1:0] | Modes                           | Packet<br>forwarding                                        | Latency                      | Switch & buffer | Max<br>length | Note                                                                                                               |

|---|--------------|---------------------------------|-------------------------------------------------------------|------------------------------|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------|

| 1 | Х            | Pure<br>converter<br>mode       | OAM: pass<br>Error: pass<br>Good: pass<br>Pause: pass       | Min                          | Un-used         | 9KB           |                                                                                                                    |

| 0 | 00           | Switch<br>mode                  | OAM: filter<br>Error: filter<br>Good: pass<br>Pause: option | Ethernet<br>Packet<br>length | Used            | 2046B         | Forward pause frame options:<br>Register 01h[5].                                                                   |

| 0 | 01           | Converter<br>mode               | OAM: filter<br>Error: pass<br>Good: pass<br>Pause: pass     | OAM<br>packet<br>length      | Un-used         | 9KB           |                                                                                                                    |

| 0 | 10           | Modified<br>cut-through<br>mode | OAM: filter<br>Error: pass<br>Good: pass<br>Pause: option   | 64 bytes                     | Used            | 2046B         | Forward pause frame options:<br>Register 01h[5].                                                                   |

| 0 | 11           | Auto<br>Converter<br>mode       | OAM: filter<br>Error: pass<br>Good: pass<br>Pause: pass     | OAM<br>packet<br>length      | Un-used         | 9КВ           | Change to modified cut-through<br>mode automatically, if duplex or<br>speed of port 1 and port 2 are not<br>equal. |

#### 3.7 Switch engine and queue management

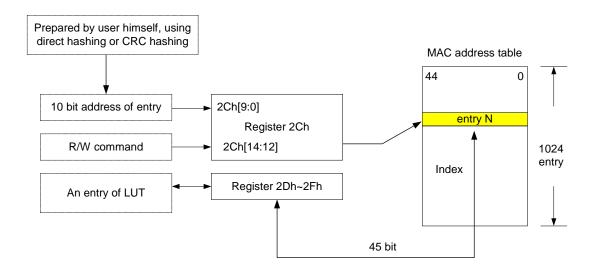

#### 3.7.1 Address learning and hashing

| Related registers | 12h[0] |

|-------------------|--------|

IP113S's switch engine can handle up to 1024 MAC address entries. And it provides two kinds of hash method to maintain the MAC address table; one is the direct mapping and the other is the CRC-12 algorithm. When the direct mapping method is selected, register 12h[0] set to "1", IP113S recognizes the least significant 12 bits of the MAC address. When the CRC-12 algorithm is used, register 12h[0] set to "0"; IP113S executes the following equation to decide the address (location) in the MAC address table.

CRC-12 equation: X^12+X^11+X^3+X^2+X+1

Packets with the following conditions will not be stored in MAC address table.

- Erroneous packet

- 802.3x pause packet

- 802.1D Reserved Group packet

- Multicast source MAC address

#### 3.7.2 Aging

| Related registers 12h[1], 13h[7:0] |

|------------------------------------|

|------------------------------------|

IP113S supports programmable aging time to meet various the system requirement, ranging from 384 sec to 98304sec  $\pm$  6.7%. User can program aging time by writing register 13h[7:0]. The address aging function can be disabled by programming register 12h[1].

# 3.7.3 Special packet handling

IP113S recognize the following type of packets by examining the field listed in the following table. Port 3 can be defined as a CPU port by writing "1" to register 12h[4].

|                         |                                        |    |      |          | Actio                                                                       | on                            |

|-------------------------|----------------------------------------|----|------|----------|-----------------------------------------------------------------------------|-------------------------------|

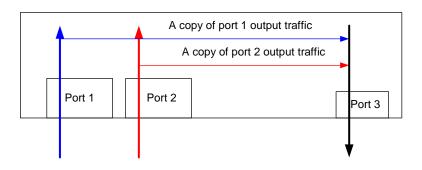

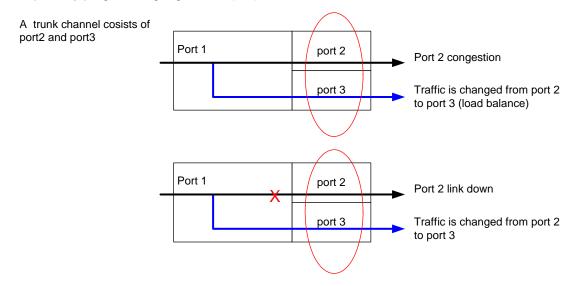

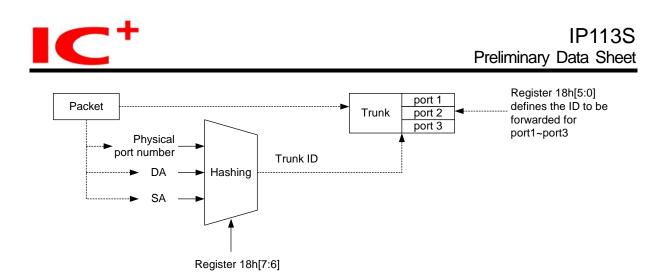

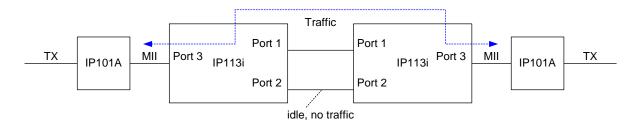

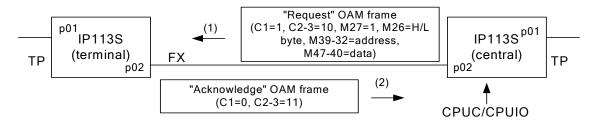

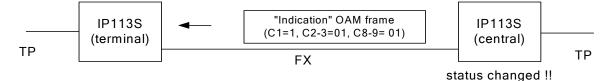

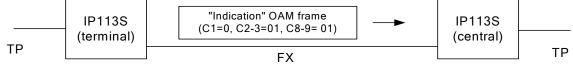

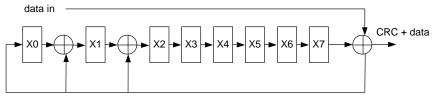

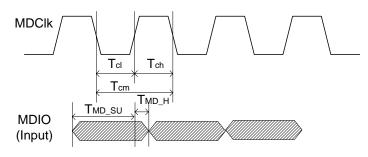

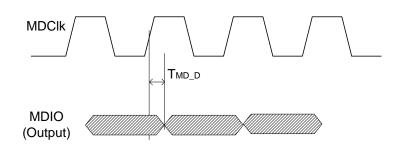

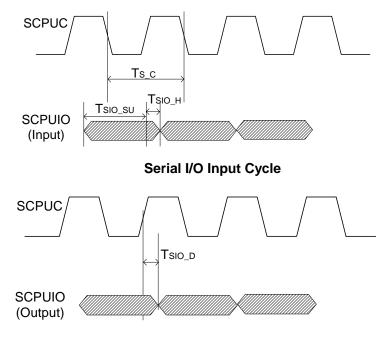

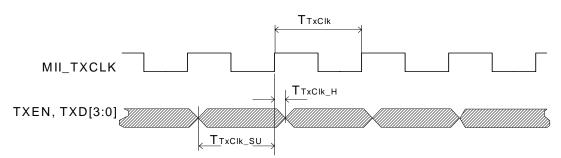

|                         | DA                                     | SA | Туре | Register | 12h[4]=1                                                                    | 12h[4]=0                      |